# Analytical Modeling of Non Planar MOSFET

by Jatmiko Endro Suseno

**Submission date:** 28-Dec-2020 03:27PM (UTC+0700)

**Submission ID: 1481631961**

File name: ArtikelC3\_JES.pdf (239.79K)

Word count: 2222

Character count: 11359

# ANALYTICAL MODELING OF NON PLANAR MOSFET

#### Jatmiko Endro Suseno

Department of Physics, Diponegoro University, Semarang, Indonesia. Email: jatmikoendrosuseno@undip.ac.id

#### Abstract

The Non Planar MOSFET structure with curved-channel is one alternative MOSFET structure for enhance the electrical performance. The study was focused on the non planar devices which has curved-channel including grooved-gate, recessed-channel, V-shaped and sidewall vertical MOSFET. The presence of corner region can effective in reducing the electric field at the drain, thus improving reliability of short channel effects (SCEs). The corner effect can reduce surface potential. It can improve the characteristic of the device electrical performance, especially the reduction of short channel effect and hot carrier effects. Therefore, the curved-channel MOSFET has a very great application prospect in deep submicron device architecture.

Keywords: MOSFET, Non Planar, curve channel, surface potential, short channel effects

#### Abstrak

MOSFET berstruktur bukan planar terutama bentuk kanal membelok merupakan salah satu alternative MOSFET untuk meningkatkan kinerja listrik divais. Studi ini difoluskan pada divais yang berbelok seperti MOSFET dengan kanal berbentuk lembah dangkal (grooved gate),lembah dangkal (recessed-channel), huruf V (V-shaped) dan kanal vertical berbelok (sidewall vertical) Keberadaan daerah pojok dapat menguranggi medan listrik pada drain serta mengurangi efek kanal pojok. Efek tersebut dapat menurunkan tegangan permukaan serta meningkatkan karakteristik kinerja listrik dari divais terutama efek kanal melengkung dan efek pembawa panas. Oleh karena itu, MOSFET kanal yang berbelok mempunyai prospek aplikasi yang sangat besar didalam pembiatan arsitektur divais berukuran sangat kecil.

Kata kunci: MOSFET, bukan planar, kanal melengkung, tegangan permukaan, efek kanal melengkung

#### Introduction

In order to keep under control the short channel effects (SCEs), Metal-Oxidemodifications ofSemiconductor Field-Effect-Transistors (MOSFETs) structures have shown to be a good alternative to traditional bulk MOSFETs. New structure devices such as grooved-gate, recessed-channel, Vshaped and vertical MOSFET [1-4] (Fig. 1). Previous works have demonstrated that, in spite of their benefits, the MOSFET with curved-channel can reduce the Short Channel Effect. The presence of the groove in recessedchannel or grooved-gate MOSFETs can enhance the electrical performance [5]. The curved structure at the channel of device is effective in reducing the electric field at the drain, thus improving reliability. Furthermore, it can also reduce the substrate current, and increase the highest applicable gate to drain voltage, so that improving the reliability of the device. phenomenon is the so called corner effects. It has been shown that corner effects are highly related to the geometrical parameters of the device, as long as to the doping density [5]. Previous works have focused on the influence of the corner effect that may affect the potential barriers for the device channel [6,7] which can improve the characteristics of the device especially the reduction of short channel effect (SCE) such as a high threshold voltage (V<sub>th</sub>), a low DIBL and GIDL effect, closeness to ideal sub-threshold slope, and a high  $I_{ON}$ – $I_{OFF}$  ratio [8-10].

#### Jatmiko Endro Suseno

#### Analytical Modeling of ...

Therefore, the main goal of this work is to carry out a thorough study of the corner effects for MOSFET which has curved-channel. To do so, we have developed a numerical simulator that self-consistently solves the Poisson equations in the structure under study. As it can be seen in Fig. 1, all device structures have the corner region in the channel, allowing a more effective control of the electrostatics in the channel.

Figure 1. Some structures of MOSFETs with curved-channel such as structures of (a) Grooved-gate,(b) V-shaped, (c) recessed-channel (d) sidewall vertical

#### Method

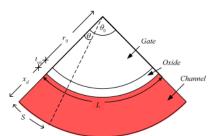

The schematic cross-section diagram of this single gate vertical sidewall MOSFET depletion layer is shown in the Figure 2.

Figure 2. The aproximation of curvedchannel MOSFET as cylindrical coordinates

This area is described by a quarter circles. For the simplified structure in

Figure 2, the 2-D Poisson equation for these areas of the device can be given as follows [2,11]:

$$\frac{\partial^2 \phi_2(r,\theta)}{\partial r^2} + \frac{1}{r} \frac{\partial \phi_2(r,\theta)}{\partial r} + \frac{1}{r^2} \frac{\partial^2 \phi_2(r,\theta)}{\partial \theta^2} = \frac{qN_A}{\varepsilon_{SS}} \tag{1}$$

where  $\phi$  is the electric potential in the active area of the device,  $\varepsilon_{\rm Si}$  is the channel silicon permittivity, and N<sub>A</sub> is the channel doping density. All the potentials of the device must consist of the same parameters, namely distances, so that for the curved-channel region,  $\phi$  (r,  $\theta$ ) can be converted into  $\phi$  (s, r) where s = r.  $\theta$ .

The s-direction is considered along the channel length and r-direction along the depletion channel thickness. We assume that the concave comer is a part of the curved area and therefore the Poisson equation for the curve area potential uses cylindrical coordinates and the s-r coordinates. The potential distributions in the depletion layer for these areas are [2,11]:

$$\varphi(r,\theta) = \varphi_s(\theta) + D_1(\theta)r + D_2(\theta)r^2 + D_3(\theta)r^3$$

(2)

where  $L_p$  is the curved-channel length  $(L_p = r \theta_0)$

The Poisson equation is solved separately for the three area regions using the following boundary conditions:

1. Potential at the depletion edge is given by:

$$\varphi(s, r_2) = \varphi_B \tag{3}$$

where  $\phi_B$  is the body electrostatic potential and  $r_2$  is position of the depletion edge, given as  $r_2 = r_0 + t_{ox} + w_{d}$ . 2. Electric flux at the depletion edge is given by:

$$\left. \frac{\partial \varphi}{\partial r} \right|_{r=r_0} = 0 \tag{4}$$

ISSN: 1410 - 9662

3. Electric flux at the interface of the gate/oxide is continuous for both the metal gates:

$$\left. \frac{\partial \varphi}{\partial r} \right|_{r=r_1} = \frac{\varepsilon_{ax}}{\varepsilon_{Si}} \left[ \frac{V_{gs}' - \varphi_{s2}[s]}{r_0 \ln(1 + t_{ox}/r_0)} \right]$$

(5)

where  $r_1$  is position of the interface of the gate/oxide,  $r_1 = r_0 + t_{ox}$ ,  $\varepsilon_{ox}$  is the dielectric constant of the oxide,  $t_{ox}$  is the gate oxide thickness,  $V_{gs}$  is the gate-to-source bias voltage,  $V_{gs}$  ' =  $V_{GS}$ - $V_{FB}$ ,  $V_{FB}$  being the flat band voltage. The gate oxide capacitance per unit area of flat region in the x-y direction and the pieshaped region in the corner are listed in

[2] as

$$C_r = \left(\frac{\varepsilon_{ox}}{r_0 \ln(1 + t_{ox}/r_0)}\right)$$

.

4. Potential at the source end is described as :

$$\varphi(x=0,y) = \varphi_{bi} \tag{6}$$

where  $\phi_{bi} = (E_g/2) + V_T \ln (N_A N_D/n_i^2)$  is the built- in potential,  $N_D$  is the source/drain doping concentration,  $E_g$  is the silicon bandgap,  $V_T$  is the thermal voltage, and  $n_i$  is the intrinsic carrier concentration.

5. Potential at the drain end is described as:

$$\varphi(r,s=L) = V_{ds} + V_{bi} + V_{sub}$$

(7)

where L is channel length,  $L=L_p$  and  $V_{DS}$  is the applied drain-source bias.

The values of the coefficients  $D_1$  to  $D_3$  in (2) can be calculated from the boundary conditions of 1 to 4.

We derived the equation for the surface potential from the Poisson equation [7] as shown here:

$$\frac{\partial^2 \varphi_s(s)}{\partial s^2} - \alpha \varphi_s(s) = \beta \tag{8}$$

The  $\alpha_i$  and  $\beta_i$  can be obtained by using boundary conditions at the source and drain.

$$\alpha = -\frac{6 r_1 \varepsilon_{Si}}{C_r r_1 r_2^2 - (r_1 - r_2)^2 \varepsilon_{Si}}$$

$$\beta_2 = (r_1 (C_r r_2^2 (9r_1^2 - 8r_1 r_2 + r_2^2) (V_{gr} - 1) - r_1 (r_2 - r_1) (N_s q r_2^2 (r_2 - 3r_1) + 6(r_1 - r_2) \varepsilon_{Si} \phi_b) / (-C_r r_1 (r_1 - r_2)^2 r_2^2 + (r_1 - r_2)^4 \varepsilon_{si})$$

The general solutions to confine the surface potential  $\phi_s$  at the gate oxide/silicon interface are listed as:

$$\varphi_s(s) = A \exp(\eta s) + B \exp(-\eta s) - \frac{\beta}{\alpha}$$

(9)

where A, B are constants and  $\eta = \sqrt{\alpha}$ . Using boundary condition of 1-4, we can obtain coefficients of A and B.

Using surface potential equation from Eq. (8), we can derive the minimum surface potential  $\varphi_{smin}$  under

condition

$$\frac{\partial \varphi_s}{\partial \theta}\Big|_{\theta=\theta_m} = 0$$

, and obtain the

angle when the minimum surface potential  $\theta_m$  as

$$\theta_m = \frac{\lambda}{2} \ln \left( \frac{\Phi_s(e^{\frac{2\theta_0}{\lambda}} - 1) - V_d}{\Phi_s(1 - e^{\frac{-2\theta_0}{\lambda}}) + V_d} \right) (10)$$

Therefore, the minimum surface potential or the potential at  $\theta_m$  is

$$\varphi_{\text{min}} = V_g - \frac{N_{eff} x_d R_t}{C_{exc} (x_d - R_t)} + \frac{1}{2Sinh \left(\frac{2\theta_0}{\lambda}\right)}$$

$$\sqrt{\left(\Phi_s \left(e^{\frac{-\tau_s}{\lambda}} - 1\right) - V_d\right) \left(\Phi_s \left(1 - e^{-\frac{\tau_s}{\lambda}}\right) + V_d\right)}$$

(11)

#### Results and Discussion

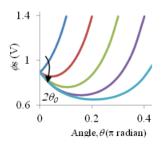

Figure 3 also shows that no minimum potential point appears in the distribution line when the corner is smaller than a critical angle. This indicates that when the corner angle is too small, n potential barrier exists and the characteristics of the grooved-gate devices are analogous to that of the

#### Jatmiko Endro Suseno

#### Analytical Modeling of ...

planar ones. When it is bigger than the critical angle, the corner effect will be observed.

Figure 3. Surface potential distribution for different corner values

The corner effect of groovedgate devices can be explained as follows: The smaller the radius of the corner, the more dispersive the electric field lines according to the theory of electric field. Because the radius of the planar part of the channel can be regarded as infinite, the electric field at the comer is very small, and the collapses of the surface potential form the barriers.

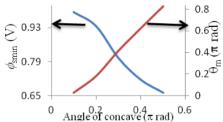

This minimum surface potential value shows the potential barrier height of the grooved gate device. These potential barrier height and minimum corner angle are shown in Fig 4 follows. From this graph, it shows that the minimum surface potential decrease with the increase of the corner angle, because the bigger the corner angle, the smaller the radius and the more heavily the surface potential collapses, giving rise to increase of the short channel effect.

Figure 4. Formation of minimum surface potential and their respective position as a function of groove corner angle.

The parameter of  $\lambda$  describes the potential distribution in the depletion layer, which in turn depends on the device geometry and boundary conditions. Hence, to operate the device as in the long channel regime, i.e., to avoid the short channel effect, the minimum channel potential should be decreased by increasing the substrate doping concentration or by reducing  $\lambda$ . The definition of  $\lambda$  implies the bigger the corner angle  $\theta_0$ , the smaller the radius  $r_0$  and the smaller the  $\lambda$ , which is called the corner effect of grooved-gate MOSFET.

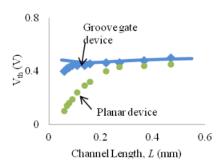

The theshold voltage (V<sub>th</sub>) rollof is shown in Fig. 5 below. The roll-off of V<sub>th</sub> is suppressed in the grooved gate MOSFETs, a reverse short-channel effect is observed, where V<sub>th</sub> becomes constant relatively, as the channel length is reduced. Further, the V<sub>th</sub> value for groove channel MOSFET structure is found to be higher than planar MOSFET structure with the same substrate doping. This implies that the maximum barrier that electrons need to overcome when traveling from source to drain.

#### **Berkala Fisika** Vol. 15, No. 4, Oktober 2012, hal 113 - 118

Figure 5. Threshold Voltage (V<sub>th</sub>) rolloff of curved channel and planar MOSFETs for modeling (solid lines) and experiment (dot lines)

#### Conclusion

The electron potential profile in the channel region having concave corner, is derived by the Poisson equation in the cylindrical coordinates. This model studies the influence of the corner effect for the single gate vertical MOSFET. The electric field of the channel in the single gate vertical MOSFET and impact on the threshold are studied. The effects of corner effect on the Short Channel Effect (SCE) reduction of this device can easily be investigated using the simple model presented in this work. The emphasis of SCE is an advantage for the MOSFET structure with curved-channel as a candidate for small scale devices in the future.

The result shows that the minimum surface potential of a curved channel MOSFET is smaller than the planar MOSFET. Thus, the curved-channel MOSFET has a higher threshold voltage for various values of Lg'. The minimum surface potential of curved-channel MOSFET is higher than that of a planar MOSFET. The corner of channel has a "coupling" of the potential barriers, due to the potential barrier increase.

#### References

- [1] Bricout, P.H. and Dubois, E. (1996). Short-Channel Effect Immunity and Current Capability of Sub-0.1 –Micron MOSFET's Using a Recessed Channel. IEEE Transactions on Electron Devices:IEEE, 43: 1251-1255.

- [2] Ju, Z.X., Xin, G., Ping, W.J., and Yue, H. (2006). Analytical analysis of surface potential for groovedgate MOSFET. Chin. Phys. Soc: IOP Publishing Ltd. 15:631-635

- [3] Farzan, B. and Salama, C. A. T. (1976). Depletion V-Groove MOS (VMOS) Power Transistors. Solid-State Electronics:Elsivier. 19:297-306.

- [4] Schulz, T., Rösner, W., Risch, L., Korbel, A. and Langmann, U. (2001). Short-Channel Vertical Sidewall MOSFETs. Trans. Electron Devices:IEEE. 48:1783-1788

- [5] Tanaka, J., Toyabe, T., Ihara, S., Kimura, S., Noda, H., and Itoh, K. (1993). Simulation of sub-0.1-μm MOSFETs with completely suppressed short-channel effect. Electron Device Letters:IEEE.14:396-399.

- [6] Hua, M. X., Yue H., Gang S. B., Xia G.H., Xia R.H., Cheng Z. J., Feng Z. J., Z.X. Ju and Z. W. Dong, Chin. Phys. Soc. and IOP Publishing Ltd, 15,195-198 (2006)

- [7] Yu H.X., Z.F. Long, H. Ru, and Z. Xing, Chin. Phys. Soc. and IOP Publishing Ltd., 16, 812-816 (2007).

- [8] Rajendran, K. and Schoenmaker, W. (2001). Modeling of minimum surface potential and sub-threshold swing for grooved-gate MOSFETs. Microelectronics Journal:Elsivier. 32:631-639.

#### Jatmiko Endro Suseno

#### Analytical Modeling of ...

- [9] Zhang, X.J., Ma, X.H., Ren, H.X., Hao, Y. and Sun, B.G. (2004) Study on 0.1 micron grooved-gate CMOS. Solid-State and Integrated Circuits Technology. Proceedings. 7th International Conference. 1:126-129

- [10] Tong, J.N., Zou, X.C., and Shen, X.B. (2004) Influence of structural parameters on the immunity of short-channel effects in groovedgate nMOSFET. Chin. Phys. Soc: IOP Publishing Ltd. 13:1816-1820.

- [11] Kang, S.M., Leblebici, Y. (1996) CMOS Digital Integrated Circuits Analysis and Design. The McGraw-Hill Co. Inc.: New York

### Analytical Modeling of Non Planar MOSFET

**ORIGINALITY REPORT**

22%

6%

20%

1%

SIMILARITY INDEX

INTERNET SOURCES

**PUBLICATIONS**

STUDENT PAPERS

#### PRIMARY SOURCES

F. G. Ruiz, A. Godoy, F. Gamiz, L. Donetti, C. Sampedro. "Study of the Corner Effects on Pi-Gate SOI MOSFETs", 2007 Spanish Conference on Electron Devices, 2007

6%

Publication

J. Tanaka, S. Kimura, H. Noda, T. Toyabe, S. Ihara. "A sub-0.1-µm grooved gate MOSFET with high immunity to short-channel effects", Proceedings of IEEE International Electron Devices Meeting, 1993

3%

Publication

web.iitd.ac.in

3%

Abhinav Kranti, S. Haldar, R.S. Gupta.

"Analytical model for threshold voltage and I–V characteristics of fully depleted short channel cylindrical/surrounding gate MOSFET",

Microelectronic Engineering, 2001

3%

Publication

X.-J. Zliang, Xiao-Hua Ma, Hong-Xia Ren, Yuc

|    | grooved-gate CMOS", Proceedings. 7th International Conference on Solid-State and Integrated Circuits Technology, 2004., 2004 Publication                                                                                                                    | 3%  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6  | www.ingentaconnect.com Internet Source                                                                                                                                                                                                                      | 2%  |

| 7  | Pradeep Agarwal. "", IEEE Transactions on Electron Devices, 3/2008 Publication                                                                                                                                                                              | 1%  |

| 8  | Kumar, M.J "Evidence for suppressed short-channel effects in deep submicron dual-material gate (DMG) partially depleted SOI MOSFETs - A two-dimensional analytical approach", Microelectronic Engineering, 200411 Publication                               | 1%  |

| 9  | M. Jagadesh Kumar, G. Venkateshwar Reddy. "Evidence for suppressed short-channel effects in deep submicron dual-material gate (DMG) partially depleted SOI MOSFETs – A two- dimensional analytical approach", Microelectronic Engineering, 2004 Publication | 1%  |

| 10 | Ping-Chang Yang, Patrick S Liu. "Modeling of anomalous current-voltage characteristics in                                                                                                                                                                   | <1% |

floating body fully depleted SOI nMOSFETs",

Solid-State Electronics, 1996

Hao, Bao-Gang Sun. "Study on 0.1 micron

# www.ijcaonline.org Internet Source

Exclude quotes Exclude matches Off Off

Exclude bibliography On

## Analytical Modeling of Non Planar MOSFET

| GRADEMARK REPORT |                  |  |

|------------------|------------------|--|

| FINAL GRADE      | GENERAL COMMENTS |  |

| /0               | Instructor       |  |

| 70               |                  |  |

|                  |                  |  |

| PAGE 1           |                  |  |

| PAGE 2           |                  |  |

| PAGE 3           |                  |  |

| PAGE 4           |                  |  |

| PAGE 5           |                  |  |

| PAGE 6           |                  |  |